お客さまの幅広い用途に合わせた製品設計を可能とし、脱炭素社会実現に貢献

2021年8月19日

株式会社日立製作所

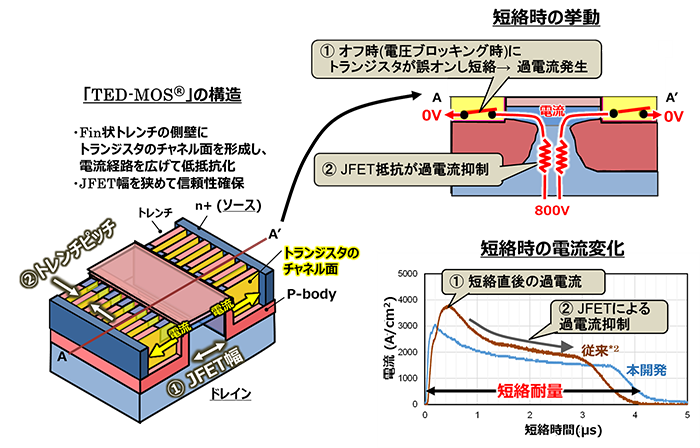

図1 「TED-MOS®」の構造、およびデバイスが短絡した際の過電流の応答特性と物理モデル

日立はこれまで、脱炭素社会の実現に向け、次世代材料の炭化ケイ素(SiC)を用いた新構造パワーデバイス「TED-MOS®」*1を開発し、その耐久性と低消費電力特性の向上を進めてきました*2*3。今回、デバイスが短絡*4した際の破壊原因となる過電流について、その抑制機構に関する物理モデルを構築しました。さらに本物理モデルに基づき、「TED-MOS®」の構造的特長を生かした高自由度なデバイス設計技術を開発しました。これにより、シリコン系の材料を含めた従来型のパワーデバイスで課題とされていた、耐久性と低消費電力特性のトレードオフを解消でき、お客さまの幅広い用途で電力機器の高効率化・省エネ化に貢献します。今後は、「TED-MOS®」のさらなる性能向上と、電力システムや電気自動車、データセンターなど幅広い用途への製品適用をめざします。

本成果の一部は2021年5月31日~6月3日に開催されたThe 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD)において発表しました。

SiCパワーデバイスは、従来のシリコン(Si)を用いたデバイスに比べ、絶縁破壊電界強度が高いため、素子膜厚を薄くすることができ、低抵抗での高速スイッチングに適しています。一方、デバイスがオフ時の絶縁破壊電界強度が高いため、誤動作で短絡が生じた際の寿命を確保しにくいという課題がありました。

今回、この課題を解決するため、図1に示した短絡時の電流の振る舞い、特に、短絡による過電流が、ピークを示した後に減衰する現象に着目し、この過電流抑制に関する物理モデルを構築しました。ここで、過電流が発生してからデバイスが破壊されずに耐えられる時間を「短絡耐量」と定義し、耐久性を表す指標として用います。デバイスが短絡する過程では、①デバイスがオフの状態(電圧がブロッキングされている状態)において、トランジスタが誤まってオンの状態になることで過電流が流れ、②デバイス中央部のJFET*5の電流密度が高まり、局所的に温度が上昇、③その温度上昇によりJFETの抵抗が増大し、過電流が減衰する、と考えられます。短絡耐量を向上させるには、デバイス破壊の原因となる過電流を抑制することが重要です。一般的に、トランジスタ抵抗が大きいほど短絡時の過電流が低く、トランジスタ抵抗と短絡耐量とはトレードオフの関係にあると考えられていました。ところが、今回着目した上記③の物理モデルに基づけば、デバイス短絡時のJFET発熱による抵抗の増大が大きい構造を実現できれば、短絡時の過電流を低減でき、トランジスタ抵抗を増大させることなく、短絡耐量の向上が可能になります。

「TED-MOS®」は、図1に示すように、トレンチピッチ(溝)に垂直・水平方向の設計パラメータが互いに独立しており、その結果、トランジスタ抵抗とJFET抵抗とを独立に設計することが可能です。この特長を生かし、上記物理モデルで得られた知見を反映したデバイス設計技術を開発しました。具体的には、デバイス短絡時の発熱を制御するパラメータとしてJFET幅を設定、一方、トランジスタ抵抗を制御するパラメータとしてトレンチピッチを設定することで、短絡耐量とオン抵抗*6(消費電力の指標)とをそれぞれ独立に設計することを試みました。トレンチピッチは「TED-MOS®」固有の設計パラメータであり、これを狭めると、トレンチの表面積と電流が流れるチャネル*7面が増え、トランジスタ抵抗が低減します。

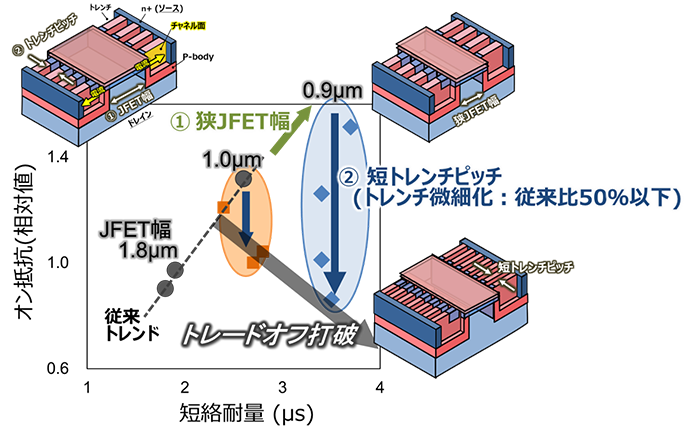

図2に示すように、実際に作成したさまざまな設計のデバイス評価結果では、オン抵抗(消費電力の指標)を縦軸、短絡耐量(耐久性の指標)を横軸としています。図2において、黒点線と黒丸で示したものが従来*2のトレードオフで、JFET幅を広げればオン抵抗は下がりますが、短絡耐量が劣化します。今回新たに得られたデータは、オレンジ色および青色で示した領域で、それぞれ、JFET幅が1.0μm, 0.9μmです。JFET幅を1.0μmから0.9μmに狭めただけでは、短絡耐量は改善するもののオン抵抗が増大します(①の矢印で示したトレンド)。しかし、JFET幅を変えず、トレンチピッチを狭めてトランジスタ抵抗を低減すると、短絡耐量を維持したままオン抵抗だけを下げられる(②の矢印で示したトレンド)ことを確認しました。オレンジ色で示したJFET幅1.0μmのサンプル群も同様で、短絡耐量を維持したままオン抵抗だけを低減しています。このように、「TED-MOS®」のデバイス構造では、JFET幅とトレンチピッチを設計パラメータとして調整することで、短絡耐量とオン抵抗とをそれぞれ独立に設計できることが確認できました。

今後は本技術を用いて、従来課題とされてきた耐久性と低消費電力性のトレードオフの関係を解消し、高い設計自由度でお客さまの幅広い用途に適合したパワーデバイスを提供し、社会インフラ製品の電力消費量低減、二酸化炭素排出量の削減により脱炭素社会の実現に貢献していきます。

図2 高自由度デバイス設計技術による、オン抵抗・短絡耐量間のトレードオフ解消