CMOS半導体プロセス親和性と量子ドット安定動作を両立

2020年4月27日

株式会社日立製作所

日立は、量子コンピュータの大規模集積化につながるシリコン半導体を用いた量子ビット*1アレイの基本構造の試作に成功しました。従来、量子コンピュータは、大規模集積化に伴い、量子ビットを動作させるための信号配線数が増えることで小型化が困難でした。本アレイでは、CMOS半導体回路技術*2を応用し、複数の量子ビットを制御する信号配線を共通化することで、配線数の増加を抑制しながら量子ビットを2次元状に配列して大規模集積化を実現することを試みました。今回、量子計算の際に電子を閉じ込める箱となる量子ドット*3をアレイ上の所望の位置に安定的に形成できることを確認しました。今後、日立は、本アレイ構造を用いて量子計算の実証に取り組み、大規模集積化が可能なシリコン量子コンピューターの開発を加速させていきます。

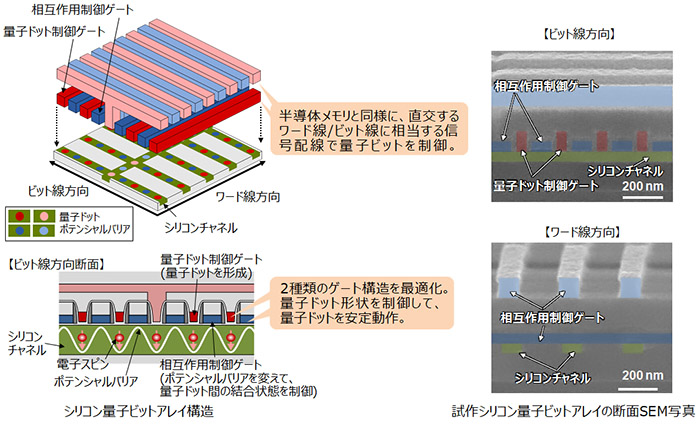

2次元シリコン量子ビットアレイ構造(左図)と試作した量子ビットアレイの断面写真(右図)

本成果は、科学誌「Applied Physics Letters」(2020年4月23日付:日本時間4月24日)にFeatured Articleとして掲載済。

本成果の一部は東京工業大学との共同研究の結果得られたものです。

量子ビット数の増加に伴い、それぞれのビットを動作させるための信号配線数が増え、小型化できないことが大規模集積化に向けた課題となっていました。本アレイでは、SRAMやDRAM*7などの半導体メモリと同様に直交するワード線/ビット線*8に相当する信号配線で、複数の量子ビットを形成する素子、および、量子ビット間の結合を制御する構造にしました。このように信号配線を共通化することで、配線数の増加を抑制しながら量子ビットの大規模集積化が可能となります。

半導体回路を用いて多数の量子ビットを安定に動作させるために、量子計算に必要となる量子ドットを形成し、制御する際の電圧マージンを確保することが課題となっていました。今回、上記した2種類のゲート電極のゲート長や位置関係などの構造と、それぞれのゲート電極に加える電圧を最適化することで、量子ドットの安定動作が可能となりました。