このニュースリリース記載の情報(製品価格、製品仕様、サービスの内容、発売日、お問い合わせ先、URL等)は、発表日現在の情報です。予告なしに変更され、検索日と情報が異なる可能性もありますので、あらかじめご了承ください。なお、最新のお問い合わせ先は、お問い合わせ一覧をご覧下さい。

2011年12月2日

株式会社日立製作所

国立大学法人神戸大学

600計算機ノードの並列処理で67万ケースのシミュレーションを約12時間で実行

株式会社日立製作所(執行役社長 : 中西 宏明/以下、日立)と国立大学法人神戸大学(学長 : 福田 秀樹/以下、神戸大学)は、このたび、産業機器、自動車やロボットなどに搭載される電子制御ユニット(Electronic Control Unit/以下、ECU)内の半導体メモリでのエラーの発生による、組み込みソフトウェア(以下、組み込みソフト)からエンジンやモーターなどのハードウェアまでの影響を、すべてコンピュータ上で検証できるクラウド型の評価・検証シミュレーション技術を開発しました。本技術をECUの開発に用いることにより、半導体メモリのエラーが組み込みソフトおよびエンジンやモーターなどのハードウェアへ及ぼす影響を短時間で検証できるようになり、メモリエラーによるシステム全体のダウンなどのリスクを低減させ、機能安全*1を考慮した効率的な制御装置の開発を実現します。

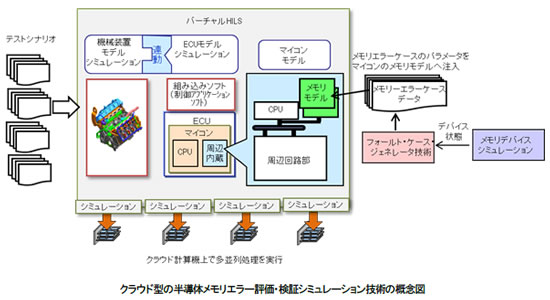

今回、開発した技術は、日立のバーチャルHILS(Hardware-in-the-Loop Simulation)*2と神戸大学のメモリデバイスシミュレーション技術を統合したシミュレーション技術であり、双方の技術を統合するために、環境温度、動作電圧や製造のバラつきなどの様々なメモリエラーケースを生成し、そのパラメータをバーチャルHILSに注入する「フォールト・ケース・ジェネレータ技術」と、膨大なエラーケースをクラウド内の多数の計算機ノードに自動的に割り振り、並列実行するクラウド型の並列計算技術を新たに開発しました。今回、600計算機ノードを用いて、1メガビットSRAMが搭載されたECUにおいて10ミリ秒周期で動作する組み込みソフトの評価・検証を行った結果、67万エラーケース(半導体メモリチップ6,000個程度に相当)のシミュレーションを約12時間で実行できる見通しを得ました。

なお、本技術は、科学技術振興機構 戦略的創造研究推進事業(CREST)の研究領域「ディペンダブルVLSIシステムの基盤技術(研究統括 : 浅井彰二郎)」の研究課題「超高信頼性VLSIシステムのためのディペンダブルメモリ*3技術(研究代表 : 吉本雅彦、神戸大学大学院 教授)」の研究において、その検証技術として開発されたものです。本技術を神戸大学が開発したディペンダブルメモリを搭載したECUに適用し、その信頼性を検証した結果、注入されたメモリエラーケースの発生率が低減し、システムに対する影響を軽減できるなどの効果を確認することができました。

省エネルギーや効率の向上のため、機能の高度化が進む産業機器、自動車やロボットなどでは、ECU内の組み込みソフトの規模が増大しており、開発コストの低減や開発期間の短縮が課題となっています。また、近年、電気・電子機器やコンピュータを用いた制御装置では、安全性を高める新たな取り組みとして機能安全規格が導入されており、これらの対応も重要な課題となっています。ECUには、マイクロコンピュータをはじめとして、数多くの半導体素子が使用されています。半導体の微細加工が進むにつれて、電磁ノイズや宇宙線などの外乱や経年劣化による素子の誤動作が懸念されおり、ECUの開発では、マイクロコンピュータの故障対策も重要な検討事項となっています。特に、コンピュータメモリには、多数の半導体素子が集積されており、どの部分でエラーが生じたか(空間情報)、組み込みソフトのどの部分を実行している最中にエラーが生じたか(時間情報)によって、制御プログラムの動きが変わってきます。この結果、ECUやその制御対象である機械装置の動作も異なってきます。安全設計をより確実なものにするには、様々なメモリエラーケースについて組み込みソフトの動作を評価することが必要ですが、実験的に検証することは困難でありました。そのため、メモリエラーの発生による、組み込みソフトウェアからエンジンやモーターなどのハードウェアまでの影響を評価・検証できるシミュレーション技術の開発が求められていました。

このような課題に対応するために、今回、神戸大学のデバイスシミュレーション技術と、日立がこれまで開発してきたバーチャルHILSを統合し、ECUの半導体メモリで発生する様々なエラーケースについて、組み込みソフトの動作にどのような影響を与えるのか、さらにその影響がECUの制御対象である機械装置にどのように関係するのかを、すべてコンピュータ上で効率的に検証できるクラウド型の評価・検証シミュレーション技術を開発しました。

具体的な技術の内容は、以下の通りです。

なお、本成果は、2011年12月3日に東京大学内の武田ホールにて行われる「ディペンダブルVLSIシステムワークショップ2011/12」にて、詳細を発表する予定です。

中央研究所 企画室 [担当 : 木下]

〒185-8601 東京都国分寺市東恋ヶ窪1丁目280番地

電話 042-327-7777(直通)

システム情報学研究科・情報科学専攻・アーキテクチャ研究室 [担当 : 吉本、川口]

〒657-8501 神戸市灘区六甲台町1-1

電話 078-803-6629

以上