## (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6556404号 (P6556404)

(45) 発行日 令和1年8月7日(2019.8.7)

(24) 登録日 令和1年7月19日(2019.7.19)

| (51) Int.Cl. |       |           | F I  |       |      |

|--------------|-------|-----------|------|-------|------|

| G06F         | 3/06  | (2006.01) | GO6F | 3/06  | 301A |

| G06F         | 13/14 | (2006.01) | G06F | 3/06  | 301Z |

| G06F         | 13/38 | (2006.01) | G06F | 13/14 | 320H |

|              |       |           | G06F | 13/38 | 350  |

請求項の数 12 (全 21 頁)

(21) 出願番号 特願2019-506878 (P2019-506878) ||(73)特許権者 000005108 (86) (22) 出願日 平成29年3月24日 (2017.3.24) 株式会社日立製作所 (86) 国際出願番号 PCT/JP2017/011969 東京都千代田区丸の内一丁目6番6号 |(74)代理人 | 110000279 (87) 国際公開番号 W02018/173245 平成30年9月27日 (2018.9.27) 特許業務法人ウィルフォート国際特許事務 (87) 国際公開日 審查請求日 平成31年1月18日 (2019.1.18) 所 (72) 発明者 黒川 碧 東京都千代田区丸の内一丁目6番6号 株 式会社日立製作所内 (72) 発明者 山崎 優太 東京都千代田区丸の内一丁目6番6号 株 式会社日立製作所内

審査官 田中 啓介

最終頁に続く

(54) 【発明の名称】 ストレージシステム及びストレージシステムのバックエンド構築方法

## (57)【特許請求の範囲】

## 【請求項1】

同一パーティションに存在可能なマスタデバイスの数が規定されている通信インターフェースに従い通信を中継するスイッチと、

前記スイッチに接続された複数の記憶デバイスと、

1以上のメモリを含んだメモリ部と、

前記メモリ部と前記スイッチとに接続された 1 以上のプロセッサであり複数のマスタデバイスを有するプロセッサ部と

### を有し、

前記スイッチは、論理的に複数のパーティションに分割され、

前記複数のパーティションは、複数の第1のパーティションと、1以上の第2のパーティションとを含み、

前記複数の第1のパーティションには、前記プロセッサ部の前記複数のマスタデバイスが複数のパス経由で接続され、前記複数の記憶デバイスは接続されず、

前記1以上の第2のパーティションには、前記複数の記憶デバイスが接続され、前記プロセッサ部は接続されず、

前記スイッチは、異なるパーティション間での転送を可能にする機能であるアドレス変換機能を有し、

前記1以上の第2のパーティションの各々に、仮想的なマスタデバイスが設けられ、

前記1以上の第2のパーティションの各々について、その第2のパーティションにおけ

る仮想的なマスタデバイスが、その第2のパーティションに接続されている全ての記憶デバイスの各々に対して初期設定を実行する、

ストレージシステム。

## 【請求項2】

前記スイッチは、1以上のプロセッサである内部プロセッサ部を有し、

前記1以上の第2のパーティションの各々について、その第2のパーティションにおける仮想的なマスタデバイスは、前記内部プロセッサ部である、

請求項1記載のストレージシステム。

## 【請求項3】

前記1以上の第2のパーティションの各々について、その第2のパーティションに接続されている全ての記憶デバイスの各々に対しての初期設定では、前記内部プロセッサ部が 、前記内部プロセッサ部が使用可能なバス番号を使用する、

請求項2記載のストレージシステム。

## 【請求項4】

前記スイッチが、前記複数の記憶デバイスにそれぞれ対応した複数のメッセージ出力先アドレスを管理しており、

前記複数のメッセージ出力先アドレスの各々は、前記メモリ部のうちの、そのアドレス に対応した記憶デバイスからのメッセージの出力先の領域のアドレスであり、

前記1以上の第2のパーティションの各々について、その第2のパーティションにおける仮想的なマスタデバイスが、その第2のパーティションに接続されているいずれかの記憶デバイスからのメッセージを検出した場合、そのメッセージを、前記複数のメッセージ出力先アドレスのうちの、そのメッセージを出力した記憶デバイスに対応したメッセージ出力先アドレスへと転送し、

前記プロセッサ部は、前記メモリ部における、前記複数のメッセージ出力先アドレスにそれぞれ対応した複数の領域の各々を、その領域にメッセージが格納されているか否かを検出するために定期的にチェックする、

請求項1記載のストレージシステム。

### 【請求項5】

前記メッセージは、前記記憶デバイスの障害に関する情報である障害情報である、 請求項 4 記載のストレージシステム。

### 【請求項6】

前記スイッチが、前記複数の記憶デバイスの各々について、メッセージ出力先アドレスの他に、前記複数のパスのうちの、メッセージの出力のために使用されるパスを管理しており、

前記1以上の第2のパーティションの各々について、仮想的なマスタデバイスが、前記検出されたメッセージを、そのメッセージを出力した記憶デバイスに対応したパス経由で出力する、

請求項4記載のストレージシステム。

## 【請求項7】

前記プロセッサ部が、前記複数の記憶デバイスのうちのいずれかの記憶デバイスにデータのI/Oコマンドの送信する場合、そのI/Oコマンドが経由するパスであるコマンドパスを、前記複数のパスの各々のリンク状態と、前記複数のパスの負荷とのうちの少なくとも1つに基づいて前記複数のパスについて決定されたパス重みに従い選択する、請求項1記載のストレージシステム。

### 【請求項8】

前記プロセッサ部が、

前記複数のパスの少なくとも1つに非接続状態のパスがある場合、前記コマンドパスを、前記複数のパスの各々のリンク状態に基づいて前記複数のパスについて決定されたパス重みに従い選択し、

前記複数のパスの負荷に偏りがある場合、前記コマンドパスを、前記複数のパスの負

10

20

30

40

荷に基づいて前記複数のパスについて決定されたパス重みに従い選択する、 請求項7記載のストレージシステム。

### 【請求項9】

前記スイッチ、前記メモリ部及び前記プロセッサ部の各々は二重化されており、

前記複数の記憶デバイスは、二重化されたスイッチである第1及び第2のスイッチの両方に接続されており、

前記第1及び第2のスイッチに、二重化されたプロセッサ部である第1及び第2のプロセッサ部がそれぞれ接続されており、

前記第1及び第2のプロセッサ部に、二重化されたメモリ部である第1及び第2のメモリ部がそれぞれ接続されており、

前記第1のメモリ部における、前記第1のプロセッサ部が使用するアドレス範囲と、前記第2のメモリ部における、前記第2のプロセッサ部が使用するアドレス範囲との少なくとも一部が重複しており、

前記第1のメモリ部における、前記第1のスイッチがサポートするアドレス範囲と、前記第2のメモリ部における、前記第2のスイッチがサポートするアドレス範囲とが異なっている.

請求項1記載のストレージシステム。

## 【請求項10】

前記通信インターフェースは、PCIe (PCI-Express)であり、

前記スイッチは、マルチルートに対応可能なPCIeスイッチであり、

前記マスタデバイスは、ルートコンプレックスであり、

前記仮想的なマスタデバイスは、仮想的なルートコンプレックスであり、

前記アドレス変換機能は、NTB(Non Transparent Bridge)である、

前記初期設定は、コンフィギュレーションアクセスに従う設定である、

請求項1記載のストレージシステム。

### 【請求項11】

前記複数の記憶デバイスは、複数のNVMe-SSDである、

請求項10記載のストレージシステム。

## 【請求項12】

ストレージシステムのバックエンドの構築方法であって、

前記ストレージシステムは、

同一パーティションに存在可能なマスタデバイスの数が規定されている通信インターフェースに従い通信を中継するスイッチと、

前記スイッチに接続された複数の記憶デバイスと、

1以上のメモリを含んだメモリ部と、

前記メモリ部と前記スイッチとに接続された1以上のプロセッサであり複数のマスタデバイスを有するプロセッサ部と を有し、

前記構築方法は、

前記スイッチを、複数の第1のパーティションと、1以上の第2のパーティションと 40 を含む複数のパーティションに論理的に分割し、

前記複数の第1のパーティションには、前記プロセッサ部の前記複数のマスタデバイスが複数のパス経由で接続され、前記複数の記憶デバイスは接続されず、

前記1以上の第2のパーティションには、前記複数の記憶デバイスが接続され、 前記プロセッサ部は接続されず、

前記スイッチは、異なるパーティション間での転送を可能にする機能であるアドレス変換機能を有し、

前記1以上の第2のパーティションの各々に、仮想的なマスタデバイスを設け、

前記1以上の第2のパーティションの各々について、その第2のパーティションにおける仮想的なマスタデバイスにより、その第2のパーティションに接続されている全ての記

10

20

30

憶デバイスの各々に対して初期設定を実行する、

構築方法。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、概して、ストレージシステムのシステム構築に関する。

【背景技術】

[0002]

複数の記憶デバイス(以下、ドライブ)を搭載したストレージシステムが知られている。ドライブとして、例えばSSD(Solid State Drive)がある。

10

[0003]

また、ドライブを接続するための通信インターフェース(プロトコル)として、NVM e (NVM (Non-Volatile Memory ) Express)が知られている。

[0004]

そこで、ストレージシステムに搭載されるSSDとして、NVMe-SSDが採用されることが予測される。NVMe SSDが採用された場合、プロセッサとSSD間の通信インターフェースとして、PCIe(PCI-Express)が採用される。具体的には、例えば、プロセッサとNVMe-SSDを、PCIeスイッチ経由で接続することが考えられる。PCIeスイッチに関する技術として、例えば、特許文献 1 ~特許文献 3 が知られている。

20

30

【先行技術文献】

【特許文献】

[0005]

【特許文献 1】US2006/0242330

【特許文献 2 】US8756360

【特許文献 3 】US9141571

【発明の概要】

【発明が解決しようとする課題】

[0006]

PCIeは、同一空間内に存在可能なマスタデバイスの数が規定されている通信インターフェースの一例である。PCIeでは、一般に、ルートコンプレックスがマスタデバイスの一例であり、エンドポイントがスレイブデバイスの一例であり、ドメインが空間の一例である。PCIeでは、同一ドメインに存在可能なルートコンプレックスは1つでありその1つのルートコンプレックスに1以上のエンドポイントを接続可能である。

[0007]

マルチルート(複数のルートコンプレックス)に接続可能なPCIeスイッチであるマルチルートPCIeスイッチが知られている。

[0008]

ストレージシステムにおいて、PCIeスイッチとしてマルチルートPCIeスイッチが採用された場合、マルチルートPCIeスイッチに、プロセッサ部(1以上のプロセッサ)が有する複数のルートコンプレックス(例えばポート)と、複数のNVMe-SSD(エンドポイント)が接続されることになる。この場合、バックエンド(プロセッサ部とNVMe-SSD間)の構成として、下記の構成A及びBを含んだ構成を採用することが考えられる。

40

(構成 A) マルチルート P C I e スイッチが、論理的に複数のパーティション(ドメイン)に区切られる。各パーティションに、プロセッサ部のルートコンプレックスと、1以上の N V M e - S S D とが接続される。1ドメインにつき1ルートコンプレックスであることを維持するためである。

(構成 B) N T B (Non Transparent Bridge) が、マルチルート P C I e スイッチに搭載される。各ルートコンプレックスを、そのルートコンプレックスが接続されているパーテ

ィションとは異なるパーティションに接続されているNVMe - SSDにアクセス可能に するためである。

## [0009]

しかし、構成A及びBを含んだバックエンド構成では、下記の課題X乃至Zがあると考えられる。

(課題 X)マルチルートPCIeスイッチに接続されている各NVMe-SSDについて、そのNVMe-SSDの初期設定を、そのNVMe-SSDが接続されているパーティションに接続されているパス経由で、プロセッサ部が行う必要がある。このため、そのパスが未接続状態又は障害状態であれば、そのNVMe-SSDの初期設定を行うことができない。

(課題 Y)プロセッサ部が使用可能なデバイス数(例えば、BDF(バス番号、デバイス番号及びファンクション番号)の数)に制限がある。そして、一般に、プロセッサ部には、マルチルートPCIeスイッチ以外のPCIデバイス(例えば、通信インターフェースデバイス)も接続される。このため、プロセッサ部が使用可能なデバイス数と同数のNVMe-SSDをマルチルートPCIeスイッチに接続したとしても、プロセッサ部は、それら全てのNVMe-SSDにアクセスすることはできない。

(課題 Z )バックエンド構成の設定(例えば、N V M e - S S D に関する設定)が、煩雑である(例えば、プロセッサ部とマルチルートP C I e スイッチとを結ぶパスの増減に依存する)。具体的には、例えば、N V M e - S S D をどのパーティションに接続するか、いずれの障害が生じたらいずれのパーティションへの切り替えを行うか等が必要である。

### [0010]

課題 X 乃至 Z のうちの少なくとも 1 つのような課題は、 P C I e に限らず、同一空間内に存在可能なマスタデバイスの数が規定されている他種の通信インターフェースが、プロセッサ部とドライブ間(バックエンド)の通信インターフェースとして採用される場合にも、あり得る。

【課題を解決するための手段】

### [0011]

ストレージシステムは、同一パーティションに存在可能なマスタデバイスの数が規定されている通信インターフェースに従い通信を中継するスイッチと、スイッチに接続された複数の記憶デバイスと、1以上のメモリを含んだメモリ部と、メモリ部とスイッチとに接続された1以上のプロセッサであり複数のマスタデバイスを有するプロセッサ部とを有するプロセッサ部とでありである。複数のパーティションに分割される。複数のパーティションと、1以上の第2のパーティションとを含む。複数の別のパーティションとは、プロセッサ部の複数のマスタデバイスが複数のパス経典である。1以上の第2のパーティションには、複数の記憶デバイスは接続されない。1以上の第2のパーティションには、現なるパーティションの話での転送を可能にする機能であるアドレス変換機能を有する。1以上の第2のパーティションの各々に、仮想的なマスタデバイスが設けられる。1以上の第2のパーティションの各々にでの第2のパーティションにおける仮想的なマスタデバイスが設けられる。1以上の第2のパーティションの各々に対して初期設定を実行する。

### 【発明の効果】

## [0012]

プロセッサ部とスイッチにおける一部の第1のパーティション間のパスが未接続状態又は障害状態であっても、各記憶デバイスに対する初期設定を行うことができる。また、接続可能な記憶デバイスの数が、プロセッサ部が使用可能なデバイス数に制限されない。また、記憶デバイスは第2のパーティションに接続されればよいので、プロセッサ部とスイッチ間のパスの増減に非依存である。

## 【図面の簡単な説明】

## [0013]

10

20

30

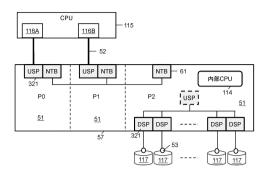

- 【図1】実施例1に係るストレージシステムのバックエンド構成の概要を示す。

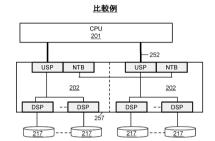

- 【図2】一比較例に係るバックエンド構成の概要を示す。

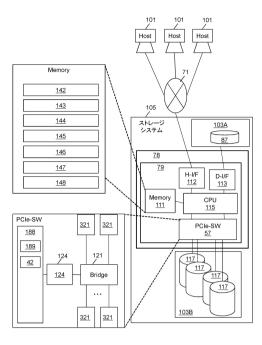

- 【図3】実施例1に係るストレージシステムを含んだ情報システムの構成を示す。

- 【図4】ドライブ状態管理テーブルの構成を示す。

- 【図5】ドライブ初期設定管理テーブルの構成を示す。

- 【図6】ドライブコンフィギュレーション管理テーブルの構成を示す。

- 【図7】パス管理テーブル146の構成を示す。

- 【図8】アドレス変換テーブルの構成を示す。

- 【図9】コマンド管理テーブルの構成を示す。

- 【図10】ドライブ初期設定処理のフローを示す。

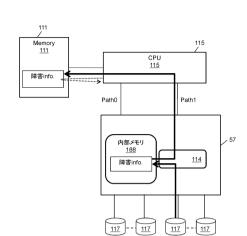

- 【図11】障害情報通知の概要を示す。

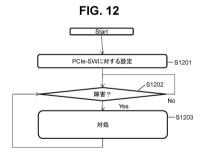

- 【図12】障害情報通知に関しCPU(ファームウェア)が行う処理のフローを示す。

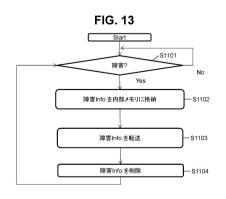

- 【図13】障害情報通知に関し内部CPU(ファームウェア)が行う処理のフローを示す

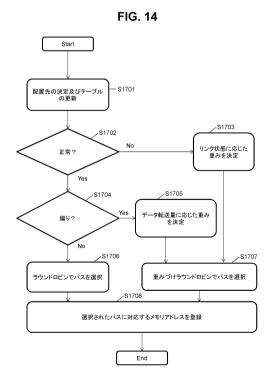

- 【図14】パス選択処理のフローを示す。

- 【図15】実施襟2に係るコントローボックスの構成の一部を示す。

- 【図16】全体アドレス管理テーブルの構成を示す。

- 【図17】第1のスイッチアドレス管理テーブルの構成を示す。

- 【図18】第2のスイッチアドレス管理テーブルの構成を示す。

- 【発明を実施するための形態】

- [0014]

以下、幾つかの実施例を説明する。

[0015]

なお、以下の説明では、「×××テーブル」といった表現にて情報を説明することがあるが、情報は、どのようなデータ構造で表現されていてもよい。すなわち、情報がデータ構造に依存しないことを示すために、「×××テーブル」を「×××情報」と言うことができる。また、以下の説明において、各テーブルの構成は一例であり、1つのテーブルは、2以上のテーブルに分割されてもよいし、2以上のテーブルの全部又は一部が1つのテーブルであってもよい。

[0016]

また、以下の説明では、「インターフェース部」は、1以上の通信インターフェースデバイスを含む。1以上の通信インターフェースデバイスは、1以上の同種のインターフェースデバイス(例えば1以上のNIC(Network Interface Card))であってもよいし2以上の異種のインターフェースデバイス(例えばNICとHBA(Host Bus Adapter))であってもよい。

[ 0 0 1 7 ]

また、以下の説明では、「メモリ部」は、1以上のメモリを含む。メモリ部に関して少なくとも1つのメモリは、揮発性メモリでよい。メモリ部は、主に、プロセッサ部による処理の際に使用される。

[0018]

また、以下の説明では、「プロセッサ部」は、1以上のプロセッサを含む。少なくとも 1つのプロセッサは、典型的には、CPU(Central Processing Unit)のようなマイク ロプロセッサである。1以上のプロセッサの各々は、シングルコアでもよいしマルチコア でもよい。プロセッサは、処理の一部または全部を行うハードウェア回路を含んでもよい

[0019]

また、以下の説明では、「ホストシステム」は、1以上の物理的なホスト計算機(例えばホスト計算機のクラスタ)であってもよいし、少なくとも1つの仮想的なホスト計算機 (例えばVM (Virtual Machine))を含んでもよい。以下、ホストシステムを、単に「ホスト」と呼ぶ。ホストは、ストレージシステムにおいてホストとして動作するVM(例

10

20

30

40

えばサーバVM)でもよい。

## [0020]

また、以下の説明では、「ストレージシステム」は、 1 以上の物理的なストレージ装置であってもよいし、少なくとも 1 つの仮想的なストレージ装置(例えば S D S (Software Defined Storage))を含んでもよい。例えば、ストレージシステムは、サーバ V M V と、ストレージコントローラとして動作する V M であるストレージ V M とを実行してもよい。ストレージ V M は、サーバ V M からの V M の V M の V M は、サーバ V M からの V M の V M であるストレージ V M は、サーバ V M からの V M の V M からの V M は、サーバ V M からの V M からの V M からの V M は、サーバ V M からの V

## [0021]

また、以下の説明では、同種の要素を区別しないで説明する場合には、参照符号(又は参照符号における共通部分)を使用し、同種の要素を区別して説明する場合は、要素のID(又は要素の参照符号)を使用することがある。

### 【実施例1】

## [0022]

図1は、実施例1に係るストレージシステムのバックエンド構成の概要を示す。

#### [0023]

CPU(プロセッサ部の一例)115が、2個のルートコンプレックス(複数のマスタデバイスの一例)116A及び116Bを有する。各ルートコンプレックス116は、例えば、ポート(以下、CPUポート)である。

## [0024]

マルチルートPCIeスイッチ(以下、PCIe-SW)57は、複数のポート(以下、SWポート)321を有する。複数のSWポート321には、下位デバイスに接続されるDSP(ダウンストリームポート)と、上位デバイスに接続されるUSP(アップストリームポート)とが含まれる。DSPは、属性がダウンストリームであるポートである。USPは、属性がアップストリームであるポートである。「下位デバイス」は、例えば、別のPCIeスイッチ(例えば別のPCIe-SW)又はエンドポイント(典型的にはドライブ117)である。「上位デバイス」は、例えば、CPU115である。

### [0025]

また、 PCIe-SW57 は、複数のパーティション(ドメイン) 5.1 に論理的に分割される。

### [0026]

本実施例では、少なくとも下記の構成が採用される。

(構成 1) P C I e - S W 5 7 に、C P U 1 1 5 が有する 2 個のルートコンプレックス 1 1 6 A 及び 1 1 6 B がそれぞれ接続される 2 個のパーティション (以下、C P U パーティション) P 0 及び P 1 に加えて、ドライブ用のパーティション (以下、ドライブパーティション) P 2 が設けられる。ドライブパーティション P 2 には、ドライブ 1 1 7 が接続され (例えばドライブ 1 1 7 のみが接続され)、少なくとも C P U 1 1 5 は接続されない。本実施例では、C P U パーティション P 0 及び P 1 の各々には、ドライブ 1 1 7 が接続されるものとする。なお、C P U パーティション P 0 及び P 1 の各々について、U S P に、パス 5 2 経由で、C P U 1 1 5 のルートコンプレックス 1 1 6 が接続される。ドライブパーティション P 2 が有する複数の D S P に、それぞれ、複数のドライブ 1 1 7 がそれぞれ有する複数のポート (以下、ドライブポート) 5 3 が接続される。

(構成 2) P C I e - S W 5 7 に、異なるパーティション 5 1 間の転送を実現するアドレス変換機能の一例である N T B (Non Transparent Bridge) 6 1 が設けられる。 N T B 6 1 が、 C P U パーティション P 0 又は P 1 とドライブパーティション P 2 間の転送を実現する。

(構成3)ドライブパーティション P 2 に、仮想的なルートコンプレックスが設けられる。本実施例では、P C I e - S W 5 7 の C P U 1 1 4 (以下、内部 C P U 1 1 4)が、ルートコンプレックスの役割を持つ。内部 C P U 1 1 4 が、各ドライブ(ドライブパーティ

10

20

40

30

ション P 2 でのエンドポイント)の初期設定を実行する。具体的には、例えば、ドライブパーティション P 2 に、仮想的な U S P が設けられ、その U S P に、仮想的なルートコンプレックス(内部 C P U 1 1 4 )が接続される。

## [0027]

図2に示す一比較例によれば、上述した構成 A 及び B 相当の構成が採用されている。このため、上述した課題 X 乃至 Z 相当の課題がある。すなわち、一比較例によれば、 C P U 2 0 1 と P C I e - S W 2 5 7 間の或るパス 2 5 2 が未接続状態又は障害状態であれば、そのパス 2 5 2 が接続されているパーティション 2 0 2 に接続されているドライブ 2 1 7 の初期設定を行うことができない。また、一比較例によれば、 C P U 2 0 1 が使用可能なデバイス数と同数のドライブ 2 1 7 を P C I e - S W 2 5 7 に接続したとしても、 C P U 2 0 1 は、それら全てのドライブ 2 1 7 にアクセスすることはできない。また、一比較例によれば、バックエンド構成の設定(例えば、ドライブ 2 1 7 に関する設定)が、 C P U 2 0 1 と P C I e - S W 2 5 7 間のパス 2 5 2 の数に依存する。

## [0028]

そこで、構成 1 によれば、 CPU1115 が接続されるパーティション 51 にはドライブ 117 が接続されない(CPU115 から見えるバス番号のドメイン内にはドライブ 117 が配置されない)。このため、CPU115 は、ドライブ 117 のために 117 のために 117 日 117 のために 117 のに 117 のと 117 のに 117 の数に 117 のない 117 のない 117 のない 117 の数に 117 のない 117 のは 117

## [0029]

また、構成 2 によれば、 C P U 1 1 5 は、 C P U パーティション P 0 又は P 1 経由で、 ドライブパーティション P 2 に接続されているドライブ 1 1 7 にアクセスできる。

### [0030]

なお、構成1(及び構成2)によれば、CPU115はドライブパーティションP2に接続されていないため、ドライブ117への初期設定(ドライブ117のコンフィギュレーションレジスタにアクセスすること)をCPU115から直接行うことができない。

## [0031]

そこで、構成3によれば、PCIe-SW57の内部CPU114が、ルートコンプレックスとして、ドライブ117に対する初期設定(ドライブ117のコンフィギュレーションレジスタにアクセスすること)をできる。

## [0032]

以下、本実施例を詳細に説明する。なお、2個のCPUパーティションP0及びP1は、複数の第1のパーティションの一例である。1個のドライブパーティションP2は、1以上の第2のパーティションの一例である。CPUパーティションの数は、CPU115が有するルートコンプレックス116の数と同数でよい。

## [0033]

図3は、実施例1に係るストレージシステムを含んだ情報システムの構成を示す。

## [ 0 0 3 4 ]

情報システムは、1又は複数のホストシステム(以下、ホスト)101と、ストレージシステム105とを有する。ホスト101とストレージシステム105は、通信ネットワーク71(例えば、SAN(Storage Area Network)又はLAN(Local Area Network))に接続される。

## [0035]

ホスト101は、ストレージシステム105にI/O(Input/Output)要求を送信する。I/O要求は、I/O先の場所を表すI/O先情報を含む。I/O先情報は、例えば、I/O先のLU(Logical Unit)のLUN(Logical Unit Number)と、そのLUにおける領域のLBA(Logical Block Address)とを含む。LUは、ストレージシステム10

10

20

30

40

20

30

40

5 から提供される論理ボリューム(論理的な記憶デバイス)である。 I / O 先情報を基に、 I / O 先の論理領域が特定され、その論理領域に基づくドライブ 1 1 7 が特定される。

### [0036]

ストレージシステム 1 0 5 は、コントローラボックス 7 8 と、コントローラボックス 7 8 に接続された 1 以上のドライブボックス 1 0 3 とを有する。

### [0037]

コントローラボックス 7 8 は、ストレージコントローラ 7 9 を有する。ストレージコントローラ 7 9 は、複数の通信インターフェースデバイス(インターフェース部の一例)と、メモリ 1 1 1 (メモリ部の一例)と、 P C I e - S W 5 7 (スイッチの一例)と、 それらに接続された C P U 1 1 5 (プロセッサ部の一例)とを有する。

## [0038]

複数の通信インターフェースデバイスは、複数のホスト101と通信するための1以上の通信インターフェースデバイスである1以上のH‐I/F112(例えば、Fibre Chan nel、iSCSI、FCoE又はPCIeのデバイス)を含む。複数の通信インターフェースデバイスは、ドライブボックス103A内のドライブ87と通信するための1以上の通信インターフェースデバイスである1以上のD‐I/F113(例えば、SASコントローラ又はPCIeスイッチ)を含んでもよい。ドライブボックス103A内の各ドライブ87は、NVMe‐SSDでもよいし、他種のPCIeドライブでもよいし、他種のSSD(例えばSAS‐SSD)でもよいし、他種のドライブ(例えばHDD(Hard Disk Drive))でもよい。

### [0039]

メモリ111は、CPU115により実行される1以上のコンピュータプログラムと、CPU115により参照又は更新される情報とを格納する。1以上のコンピュータプログラムは、例えば、ファームウェア142のようなマイクロプログラムを含む。情報は、例えば、複数のテーブルである。複数のテーブルは、例えば、ドライブ実装状態管理テーブル143、ドライブ設定状態管理テーブル144、ドライブ初期設定管理テーブル145、パス管理テーブル146、アドレス変換テーブル147及びコマンド管理テーブル148を含む。また、メモリ111には、ホスト101からのI/O要求に応答してドライブ117(又は87)に入出力されるデータであるユーザデータが一時的に格納されるキャッシュ領域が設けられる。

### [0040]

PCIe-SW57は、複数のSWポート321と、ブリッジ121と、内部CPU114(内部プロセッサ部の一例)と、内部メモリ188(内部メモリ部の一例)とを有する。

## [0041]

ブリッジ121に、複数のSWポート321が接続されている。内部CPU114に、 内部メモリ188とブリッジ121とが接続されている。内部CPU114と、SWポート321に接続されているデバイス間の通信は、ブリッジ121経由である。

### [0042]

内部メモリ188は、内部CPU114により実行される1以上のコンピュータプログラムと、内部CPU114により参照又は更新される情報とを格納する。1以上のコンピュータプログラムは、例えば、ファームウェア189のようなマイクロプログラムを含む。情報は、例えば、1以上のテーブル(例えば、後述のメッセージ通知管理テーブル42)である。

### [0043]

1以上のドライブボックス103は、少なくとも、PCIe-SW57に接続される複数のドライブ117を有するドライブボックス103Bを含む。ドライブ117は、NVMe-SSDである。ドライブ117は、他種のPCIeドライブでもよい。1以上のドライブボックス103Aを含んでもよい。

## [0044]

図4は、ドライブ実装状態管理テーブル143の構成を示す。

## [0045]

ドライブ実装状態管理テーブル143は、各ドライブ117の実装状態に関する情報を保持するテーブルである。ドライブ実装状態管理テーブル143は、ドライブパーティションP2におけるDSP毎にエントリを有する。各エントリが、ドライブ#401、実装状態402及びリンク状態403といった情報を保持する。

#### [0046]

ドライブ#401は、ストレージシステム105のプログラムが管理しているドライブ 番号である。

#### [0047]

実装状態402は、ドライブ117がDSPに対して実装(物理的に接続)されているか否かを示す。実装状態402の値として、"1"は、実装を意味し、"0"は、未実装を意味する。

## [0048]

リンク状態 4 0 3 は、ドライブ 1 1 7 が D S P に対してリンクアップ(通信可能な状態)か否かを示す。リンク状態 4 0 3 の値として、" 1 "は、リンクアップを意味し、" 0"は、リンクダウン(通信不可能な状態)を意味する。

## [0049]

図5は、ドライブ設定状態管理テーブル144の構成を示す。

### [0050]

ドライブ設定状態管理テーブル144は、各ドライブ117の設定状態に関する情報を保持するテーブルである。ドライブ設定状態管理テーブル144は、ドライブパーティションP2におけるDSP毎にエントリを有する。各エントリが、ドライブ#501、完了状態502及び結果状態503といった情報を保持する。

#### [0051]

ドライブ # 5 0 1 は、ストレージシステム 1 0 5 のプログラムが管理しているドライブ 番号である。

## [0052]

完了状態 5 0 2 は、ドライブ 1 1 7 に対する初期設定が完了したか否かを示す。完了状態 5 0 2 の値として、" 1 " は、完了を意味し、" 0 " は、未完了を意味する。

### [0053]

結果状態 5 0 3 は、ドライブ 1 1 7 に対する初期設定が完了した結果として成功か否かを示す。結果状態 5 0 3 の値として、" 1 " は、成功を意味し、" 0 " は、失敗を意味する。

## [0054]

図6は、ドライブ初期設定管理テーブル145の構成を示す。

### [0055]

ドライブ初期設定管理テーブル145は、各ドライブ117のコンフィグレーションレジスタに設定する情報を保持するテーブルである。ドライブ初期設定管理テーブル145は、ドライブパーティションP2におけるDSP毎にエントリを有する。各エントリが、ドライブ#601、バス#602、デバイス#603、ファンクション#604、ベースアドレスレジスタ605及びMSI(Message Signaled Interrupt)テーブルレジスタ606といった情報を保持する。

## [0056]

ドライブ#601は、ストレージシステム105のプログラムが管理しているドライブ 番号である。

### [0057]

バス#602は、BDFのうちのバス番号である。デバイス#603は、BDFのうちのデバイス番号である。ファンクション#604は、BDFのうちのファンクション番号である。このBDFは、CPU115が使用可能なBDFのうちのBDFではなく、内部

10

20

30

40

20

30

40

50

CPU114が使用可能なBDFのうちのBDFであり、ドライブ117のコンフィギュレーションレジスタに設定される。

### [0058]

ベースアドレスレジスタ605は、ドライブ117に対応したアドレス(CPU115のメモリマップ空間におけるアドレス)を示す。ドライブ117のコンフィギュレーションレジスタは、例えば、ドライブ117が有する記憶領域(例えば、ドライブポート53(図1参照)のレジスタ)でよい。

## [0059]

MSIテーブルレジスタ606は、ドライブ117に対応したメッセージ(例えば、ドライブ117の障害に関する障害情報)の出力先のアドレス(例えば、メモリ111における領域のアドレス)を示す。

ける領域のアドレス)を示す。 【0060】

## 図 7 は、パス管理テーブル 1 4 6 の構成を示す。 【 0 0 6 1 】

パス管理テーブル 1 4 6 は、 C P U 1 1 5 と P C I e - S W 5 7 間のパスに関する情報を保持するテーブルである。パス管理テーブル 1 4 6 は、パス 5 2 毎にエントリを有する。各エントリが、パス # 7 0 1、データ転送量 7 0 2、リンク状態 7 0 3 及び重み 7 0 4 といった情報を保持する。

## [0062]

パス#701は、パス52の識別番号である。データ転送量702は、パス52の負荷の一例であり、そのパス52を経由のデータ転送量(例えば単位時間当りの転送量)を示す。リンク状態703は、パス52のリンク状態を示す。リンク状態703として、"1"は、正常(接続状態)を意味し、"0"は、異常(未接続状態又は障害状態)を意味する。重み704は、パス52の重みを示す。

#### [0063]

図8は、アドレス変換テーブル147の構成を示す。

### [0064]

アドレス変換テーブル 1 4 7 は、変換前後のアドレス関係に関する情報を保持する。アドレス変換テーブル 1 4 7 は、ドライブ 1 1 7 初期設定処理後に C P U 1 1 5 により発行された I / O コマンド毎にエントリを有する。各エントリが、タグ # 8 0 1、パス # 8 0 2、実メモリアドレス 8 0 3 及びコマンド指定メモリアドレス 8 0 4 といった情報を保持する。なお、ドライブ初期設定処理後に C P U 1 1 5 により発行された管理対象のコマンドとして、本実施例では、 I / O コマンドが採用されているが、 I / O コマンドに加えて他種のコマンドも管理対象とされてよい。

## [0065]

タグ#801は、I/Oコマンドに関連付けられたタグの識別番号(実質的にI/Oコマンドの識別番号)である。パス#802は、I/Oコマンドが経由するパス52の識別番号である。実メモリアドレス803は、アドレス変換前のアドレス、具体的には、I/Oコマンドに従うI/O対象のユーザデータが格納されている領域(メモリにおける領域)のアドレスを示す。コマンド指定メモリアドレス804は、アドレス変換後のアドレス、具体的には、I/Oコマンドで指定されるメモリアドレス(例えば、CPU115のメモリマップ空間における宛先ドライブ対応アドレス)を示す。

### [0066]

図9は、コマンド管理テーブル148の構成を示す。

### [0067]

コマンド管理テーブル 1 4 8 は、I / Oコマンドに関する情報を保持するテーブルである。コマンド管理テーブル 1 4 8 は、ドライブ初期設定処理後にC P U 1 1 5 により発行されたI / Oコマンド毎にエントリを有する。各エントリが、タグ # 9 0 1、ドライブ # 9 0 2、レングス 9 0 3、コマンド指定メモリアドレス 9 0 4 及びドライブアドレス 9 0 5 といった情報を保持する。

20

30

40

[0068]

タグ#901は、I/Oコマンドに関連付けられたタグの識別番号(実質的にI/Oコマンドの識別番号)である。ドライブ#902は、I/Oコマンドに従うI/O先ドライブ117の識別番号である。レングス903は、I/Oコマンドに従うI/O対象のユーザデータのデータ長を示す。コマンド指定メモリアドレス904は、I/Oコマンドで指定されるメモリアドレスを示す。ドライブアドレス905は、I/O先ドライブ117におけるI/O先領域のアドレス(例えば L BA(Logical Block Address))を示す。

[0069]

以下、本実施例で行われる幾つかの処理を説明する。

[0070]

< ドライブ初期設定 >

[0071]

図10は、ドライブ初期設定処理のフローを示す。

[0072]

CPU115(ファームウェア142)が、ドライブ117に関する状態の問合せであるドライブ問合せを、PCIe-SW57に送信する(S501)。

[0073]

内部CPU114(ファームウェア142)が、ドライブ問合せに応答して、ドライブパーティションP2におけるDSP毎のドライブ情報(ドライブ#、実装か未実装か、リンクアップかリンクダウンか、設定完了か否か、及び、設定成功か否かを示す情報)をCPU115に返す(S502)。

[0074]

CPU115(ファームウェア142)が、内部CPU114からの情報(ドライブパーティションP2におけるDSP毎のドライブ情報)を、ドライブ実装状態管理テーブル143及びドライブ設定状態管理テーブル144に登録する(S503)。

[0075]

CPU115(ファームウェア142)が、テーブル143及び144を基に、1以上の未設定ドライブ117があるか否かを判断する(S504)。「未設定ドライブ117」は、実装状態402 "1"、リンク状態403 "1"及び完了状態502 "0"に対応したドライブ117である。なお、「未設定ドライブ117」は、更に、結果状態503 "0"に対応したドライブ117でよい。初期設定に失敗したドライブ117に対して初期設定をリトライするためである。

[0076]

S 5 0 4 の判断結果が真の場合(S 5 0 4 : Y e s )、 C P U 1 1 5 (ファームウェア 1 4 2 )が、1以上の未設定ドライブ 1 1 7 から選択した 1 つのドライブ 1 1 7 である対象ドライブ 1 1 7 について、初期設定指示を、P C I e - S W 5 7 に送信する。初期設定指示には、対象ドライブ 1 1 7 のドライブ # が関連付けられる。

[0077]

内部CPU114(ファームウェア189)が、その初期設定指示に応答して、対象ドライブ117に対して初期設定を実行する(S506)。具体的には、例えば、内部CPU114(ファームウェア189)は、CPU115(ファームウェア142)が定義したドライブ初期設定管理テーブル145で指示されたBDFと、ベースアドレスレジスタと、MSIテーブルレジスタとを含んだ情報を、対象ドライブ117のコンフィギュレーションレジスタに設定する。

[0078]

内部 C P U 1 1 4 (ファームウェア 1 8 9 )が、その実行結果を C P U 1 1 5 に返す ( S 5 0 7 )。その実行結果は、その設定した情報 ( B D F 、ベースアドレスレジスタ及び M S I テーブルレジスタ)と、初期設定の成否を表す情報と、対象ドライブ 1 1 7 のドライブ # とを含む。

[0079]

20

30

40

50

CPU115(ファームウェア142)が、返却された実行結果に含まれている情報(ドライブ#、BDF、ベースアドレスレジスタ及びMSIテーブルレジスタを含んだ情報)を、対象ドライブに対応したエントリ(ドライブ初期設定管理テーブル145におけるエントリ)に、登録する(S508)。

### [0800]

CPU115(ファームウェア142)が、返却された実行結果に、成功を表す情報が含まれているか否かを判断する(S509)。

### [0081]

S 5 0 9 の判断結果が真の場合(S 5 0 9: Y e s)、C P U 1 1 5 (ファームウェア 1 4 2 )が、対象ドライブ 1 1 7 に対応したエントリ(ドライブ設定状態管理テーブル 1 4 4 におけるエントリ)に、完了状態 5 0 2 " 1 "及び結果状態 5 0 3 " 1 "を登録する(S 5 1 0 )。その後、処理が、S 5 0 4 に戻る。

#### [0082]

S 5 0 9 の判断結果が偽の場合(S 5 0 9: N o)、C P U 1 1 5 (ファームウェア 1 4 2)が、対象ドライブ 1 1 7 に対応したエントリ(ドライブ設定状態管理テーブル 1 4 におけるエントリ)に、完了状態 5 0 2 " 1 "及び結果状態 5 0 3 " 0 "を登録する(S 5 1 1)。その後、処理が、S 5 0 4 に戻る。

#### [0083]

以上のように、ドライブ初期設定処理では、CPU115が使用可能なBDFがドライブ117の初期設定について使用(消費)されず、内部CPU114が使用可能なBDFがドライブ117に対する初期設定で使用される。CPU115は、初期設定が完了(且つ成功)したドライブ117のコンフィギュレーションレジスタに、そのドライブ117に対応したベースアドレス(内部CPU114が使用したベースアドレス)を用いて、アクセスすることができる。

#### [0084]

<障害情報通知>

### [0085]

ドライブパーティションP2には、CPU115は接続されていない。ドライブパーティションP2において、内部CPU114が、仮想的なルートコンプレックス(例えばルートコンプレックス)である。このため、ドライブ117が、ドライブ117の障害を検出した場合、ルートコンプレックスである内部CPU114宛に障害情報(メッセージの一例)が発行される。しかし、ドライブパーティションP2に接続されていないCPU115には、その障害情報は届かない(課題1)。CPU115から見えるバス番号のドメイン内にはドライブ117が配置されていないためである。

## [0086]

課題1を解決する方法として、内部CPU114が、ドライブ117からの障害情報を検出した場合に、CPU115に割込みで障害を通知する方法が考えられる。しかし、その方法では、割込みを受けたCPU115の処理が中断するので、1個のドライブ117の障害が、ストレージシステム105全体に影響を及ぼすことになり得る(課題2)。CPU115には、バックエンドのPCIe-SW57だけでなく、H-I/F112のような他のデバイスも接続されているためである。

## [0087]

課題2を解決する方法として、CPU115が、PCIe-SW57の内部CPU114に対して定期的に障害問合せ(いずれかのドライブ117で障害が発生したか否かの問合せ)を発行する方法が考えられる。しかし、障害問合せは、CPU115とPCIe-SW57間のパス52を経由するため、ドライブ117に対するI/Oの性能が低下する可能性もある。

### [0088]

そこで、本実施例では、図11に示すように、ドライブ117からの障害情報が、内部 メモリ188に格納され、その障害情報は、内部CPU114(又はDMA(Direct Mem ory Access))により、内部メモリ188から、メモリ111に転送され格納される。 CPU115は、内部メモリ188に代えて、メモリ111に、障害情報の有無をチェックするために定期的にアクセスする。これにより、障害情報の有無のチェックのためにパス52が使用されないので、ドライブ117に対するI/Oの性能の低下を避けることができる。

## [0089]

以下、障害情報通知に関し、CPU115及び内部CPU114の各々が行う処理のフローを説明する。なお、障害情報は、障害が発生した部位(例えばドライブ#)を示す情報と、障害の詳細を示す情報とを含む。

#### [0090]

図 1 2 は、障害情報通知に関し C P U 1 1 5 (ファームウェア 1 4 2 ) が行う処理のフローを示す。

#### [0091]

内部メモリ188内に、メッセージ通知管理テーブル42が格納されている。メッセージ通知管理テーブル42は、障害情報のようなメッセージの出力先に関する情報をドライブ117毎(DSP毎)に保持するテーブルである。CPU115が、PCIe-SW57のメモリ内のメッセージ通知管理テーブル42に、ドライブ117毎の情報を設定する(S1201)。ドライブ117毎の情報は、ドライブ#(ドライブ117の識別番号)、MSIテーブルレジスタ(ドライブ117からの障害情報の転送先領域(メモリにおける領域)のアドレス)、及び、パス#(その障害情報の転送に使用されるパスのパス#)を含む。メッセージの通知のために使用されるパスが、複数のドライブ117に均等に分散されていれば、メッセージ通知のために特定のパスに負荷が集中することを避けることが期待できる。

#### [0092]

CPU115は、メモリ111の各領域(MSIテーブルレジスタ606が示す領域)を、その領域にメッセージ(例えば障害情報)が格納されているか否かを検出するために定期的にチェック(参照)する(S1202)。

### [0093]

いずれかの領域に障害情報が格納されていることを検出した場合(S1202:Yes)、CPU115は、その領域から障害情報を取得し、その障害情報を基に障害対処処理を実行する(S1203)。例えば、CPU115は、その障害情報を基に特定されたドライブ117である障害ドライブ117に対するI/Oを停止し、その障害ドライブ117を閉塞する。

## [0094]

図13は、障害情報通知に関し内部CPU114(ファームウェア189)が行う処理のフローを示す。

## [0095]

内部 C P U 1 1 4 は、いずれかのドライブ1 1 7 の障害を検出した場合(S 1 1 0 1 : Y e s )、そのドライブ1 1 7 からの障害情報を、内部メモリ1 8 8 に格納する(S 1 1 0 2 )。内部メモリ1 8 8 内の障害情報は、メッセージ通知管理テーブル4 2 を基に、内部メモリ1 8 8 から、障害ドライブ1 1 7 に対応したM S I テーブルレジスタが示す領域(メモリ1 1 1 内の領域)に、障害ドライブ1 1 7 に対応したパス5 2 経由で、内部 C P U 1 1 4 (又は D M A)により転送される(S 1 1 0 3 )。内部 C P U 1 1 4 は、転送された障害情報を内部メモリ1 8 8 から削除する(S 1 1 0 4 )。

### [0096]

< パス選択 >

### [0097]

CPU115と各ドライブ117間に複数のパス52が存在する。ドライブ117へのI/Oコマンドで指定するメモリアドレスにより、そのI/Oコマンドが経由するパスを決定する必要がある。

10

20

30

40

20

30

40

50

[0098]

そこで、本実施例では、パス管理テーブル146(データ転送量702及びリンク状態703のうちの少なくとも1つに基づき)、I/Oコマンドで指定するパスとメモリアドレスの関係が決定される。

[0099]

以下、パス選択処理を説明する。なお、CPU115(ファームウェア142)は、パスのデータ転送量及びリンク状態を定期的にチェックしてパス管理テーブル146にチェック結果を登録するようになっている。

[0100]

図14は、パス選択処理のフローを示す。

[0101]

CPU1115(ファームウェア142)が、I/O要求に従うユーザデータの配置先領域(メモリ111における領域)を決定する(S1701)。 CPU1115(ファームウェア142)が、アドレス変換テーブル147におけるエントリ(そのI/Oコマンドに対応したエントリ)に、その配置先領域を示す実メモリアドレス803と、そのユーザデータのI/OのためのI/Oコマンドのタグ#801とを登録する。また、CPU1115(ファームウェア142)が、コマンド管理テーブル148におけるエントリ(そのI/Oコマンドに対応したエントリ)に、そのI/Oコマンドのタグ#901と、ユーザデータのI/O先のドライブ117のドライブ#902と、ユーザデータのデータ長を示すレングス903と、ユーザデータのI/O先のドライブアドレス905とを登録する。

[0102]

CPU115(ファームウェア142)が、各パスのリンク状態703が"1"(正常)か否かを判断する(S1702)。

[0103]

S 1 7 0 2 の判断結果が偽の場合(少なくとも 1 つのパスのリンク状態 7 0 3 が " 0 " の場合) (S1702:No)、CPU115(ファームウェア142)が、リンク状態 7 0 3 " 1 "のパスについての重みとして、リンク状態 7 0 3 " 0 "よりも高い重みをパ ス管理テーブル146に設定する(S1703)。なお、その際、CPU115(ファー ムウェア142)が、リンク状態703"1"に対応したパスの重みを、それらのパスの 各々のデータ転送量702に基づき、調整してよい。例えば、データ転送量702が高い 程高い重みとしてよい。S1703の後、CPU115(ファームウェア142)が、重 みづけラウンドロビンに従いパスを決定、すなわち、パスの重みの比率に基づきパスを決 定する(S1707)。例えば、パス0とパス1の重みの比が1:2の場合、パス1が2 回選択された後にパス0が1回選択される。S1707の後、CPU115(ファームウ ェア142)が、選択したパスに対応したメモリアドレスを決定し、アドレス変換テーブ ル147及びコマンド管理テーブル148を更新する(S1708)。すなわち、CPU 115(ファームウェア142)が、アドレス変換テーブル147におけるエントリ(I ノ O コマンドに対応するエントリ)に、選択したパスのパス # 8 0 2 と、選択したパスに 対応するメモリアドレスであるコマンド指定メモリアドレス804とを登録する。また、 CPU115(ファームウェア142)が、コマンド管理テーブル148におけるエント リ(I/Oコマンドに対応するエントリ)に、選択したパスに対応するメモリアドレスで あるコマンド指定メモリアドレス904を登録する。

[0104]

S 1 7 0 2 の判断結果が真の場合(全てのパスのリンク状態 7 0 3 が " 1 " の場合)(S 1 7 0 2 : Y e s )、 C P U 1 1 5 (ファームウェア 1 4 2 )が、リンク状態 7 0 3 " 1 "のパスについてのデータ転送量 7 0 2 に偏りがあるか否かを判断する(S 1 7 0 4 )。ここで言う「偏り」は、例えば、パス管理テーブル 1 4 6 のうちの最大のデータ転送量 7 0 2 と最小のデータ転送量 7 0 2 と最小のデータ転送量 7 0 2 と最小のデータ転送量 7 0 2 との差が所定値以上であることでよい。

[0105]

S 1 7 0 4 の判断結果が偽の場合(S 1 7 0 4 : N o ) 、 C P U 1 1 5 (ファームウェ

20

30

40

50

ア142)が、パス管理テーブル146に、データ転送量702(パスの負荷)が比較的低いパスの重みとして比較的高い重みを設定し、データ転送量702が比較的高いパスの重みとして比較的低い重みを設定する(S1705)。S1705の後、上述したS1707及びS1708が行われる。

## [0106]

S 1 7 0 4 の判断結果が真の場合(S 1 7 0 4 : Y e s )、 C P U 1 1 5 (ファームウェア 1 4 2 )が、ラウンドロビンに従いパスを決定する(S 1 7 0 6 )。 S 1 7 0 6 の後、上述した S 1 7 0 8 が行われる。

## 【実施例2】

[0107]

実施例2を説明する。その際、実施例1との相違点を主に説明し、実施例1との共通点について説明を省略又は簡略する。

#### [0108]

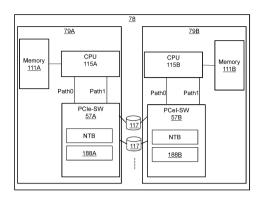

図15は、実施襟2に係るコントローボックスの構成の一部を示す。

### [0109]

コントローラボックス 7 8 は、二重化されたストレージコントローラ 7 9 としての第 1 及び第 2 のストレージコントローラ 7 9 A 及び 7 9 B を有する。従って、 P C I e - S W 5 7 も二重化されている。第 1 及び第 2 の P C I e - S W 5 7 A 及び 5 7 B に、複数のドライブ 1 1 7 が接続されている。

## [0110]

第1のメモリ111Aにおける、第1のCPU115Aが使用するアドレス範囲と、第2のメモリ111Bにおける、第2のCPU115Bが使用するアドレス範囲との少なくとも一部が重複している。具体的には、例えば、第1及び第2のCPU115A及び115Bは、それぞれ、ユーザデータやテーブルを、第1及び第2のメモリ111A及び111Bの同一アドレス範囲に格納することができる。

### [0111]

第1及び第2のPCIe - SW57A及び57Bの各々において、各ドライブ117は CPU115が接続されているCPU110ーティションに接続されてないものの、SAS(Serial Attached SCSI)又はFC(Fibre Channel)と異なり、CPU115、メモリ11、PCIe-SW57及びドライブ117の各々が、PCIeという同一の通信インターフェースで通信できる。

## [0112]

ここで、もし、或るドライブ117が暴走すると、そのドライブ117の暴走の影響により、両方のメモリ111A及び111Bの同一のアドレスに対して不正なアクセスがされ、その同一のアドレスが示す両方の領域内のデータ(例えば、ユーザデータの少なくとも一部、又は、1以上のテーブルのうちの少なくとも一部)が破壊され得る。結果として、システムダウンが生じ得る。

### [0113]

各PCIe-SW57には、NTBが設けられている。NTBは、アドレス変換を行う。このため、メモリへのアクセス先アドレスが、NTBが使用可能なアドレス範囲外のアドレス(サポート範囲外のアドレス)であれば、PCIe-SW57によって、ドライブ117の暴走によってメモリへ不正なアクセスが生じることを防ぐことができる。しかし、メモリへのアクセス先アドレスが、サポート範囲内のアドレスの場合その不正なアクセスを防ぐことはできない。

### [0114]

そこで、本実施例では、第1のPCIe-SW57Aがサポートする第1のアドレス範囲と第2のPCIe-SW57Bがサポートする第2のアドレス範囲と異なる。第1及び第2のアドレス範囲は一部の重複も無いことが望ましい。これにより、第1のメモリ11Aへのアクセス先アドレスが第1のアドレス範囲内であったとしても、第2のメモリ11Bへの同一アクセス先アドレスは第2のアドレス範囲外となる。結果として、システ

ムダウンが生じる可能性を軽減することができる。

## [0115]

具体的には、例えば、下記の通りである。

### [0116]

第1及び第2のCPU115A及び1115Bにそれぞれ接続された第1及び第2のメモリ111A及び111Bの各々が、図16に示す全体アドレス管理テーブル1600を格納する。全体アドレス管理テーブル1600は、パス毎にエントリを有する。各エントリが、CTL#1601、パス#1602、スタートアドレス1603及びサイズ1604といった情報を保持する。CTL#1601は、パスを含んだストレージコントローラ79A又は79Bの識別番号である。パス#1602は、パスの識別番号である。スタートアドレス1603は、パスに対応したアドレス範囲の開始アドレス(メモリアドレス)である。サイズ1604は、アドレス範囲のサイズである。スタートアドレス1603及びサイズ1604により、アドレス範囲が定義される。

## [0117]

第1のPCIe - SW57Aの内部メモリ188Aが、図17に示す第1のスイッチアドレス管理テーブル1700Aを格納する。第1のスイッチアドレス管理テーブル1700Aは、第1のPCIe - SW57Aに接続されているパス毎にエントリを有する。各エントリが、パス#1701A、スタートアドレス1702A及びサイズ1703Aといった情報を保持する。パス#1701Aは、パスの識別番号である。スタートアドレス1702Aは、パスに対応したアドレス範囲の開始アドレス(メモリアドレス)である。サイズ1703Aは、アドレス範囲のサイズである。スタートアドレス1702A及びサイズ1703Aにより、第1のPCIe - SW57Aがサポートするアドレス範囲が定義される。

#### [0118]

第2のPCIe - SW57Bのメモリ188Bが、図18に示す第2のスイッチアドレス管理テーブル1700Bを格納する。第2のスイッチアドレス管理テーブル1700Bの構成は、第1のスイッチアドレス管理テーブル1700Bは、第2のPCIe - SW57Bに接続されているパス毎にエントリを有し、各エントリが、パス#1701B、スタートアドレス1702B及びサイズ1703Bといった情報を保持する。

### [0119]

図16~図18のテーブル1600、1700A及び1700Bによれば、第1のPCIe-SW57Aがサポートする第1のアドレス範囲(メモリ111Aにおける領域のアドレス範囲)と、第2のPCIe-SW57Bがサポートする第2のアドレス範囲(メモリ111Bにおける領域のアドレス範囲)が異なる。これにより、上述したように、第1のメモリ111Aへのアクセス先アドレスが第1のアドレス範囲内であったとしても、第2のメモリ111Bへの同一アクセス先アドレスは第2のアドレス範囲外となる。結果として、システムダウンが生じる可能性を軽減することができる。

## [0120]

以上、幾つかの実施例を説明したが、これらは本発明の説明のための例示であって、本発明の範囲をこれらの実施例にのみ限定する趣旨ではない。本発明は、他の種々の形態でも実行することが可能である。例えば、本発明は、PCIe-SW57に代えて、同一ドメインに存在可能なマスタデバイスの数が規定されている通信インターフェースに従い通信を中継する他種のスイッチが採用されても、適用することができる。

### 【符号の説明】

## [0121]

105...ストレージシステム

20

10

30

【図3】

## 【図1】

FIG. 1

## 【図2】

FIG. 2

FIG. 3

## 【図4】

FIG. 4

ドライブ実装状態管理テーブル <u>143</u>

| ドライブ#<br><u>401</u> | 実装状態<br><u>402</u> | リンク状態<br><u>403</u> |

|---------------------|--------------------|---------------------|

| 0                   | 1                  | 1                   |

| 1                   | 1                  | 1                   |

| 2                   | 0                  | 0                   |

|                     |                    |                     |

## 【図7】

FIG. 7

パス管理テーブル <u>146</u>

| Path#<br><u>701</u> | データ転送量 [MB/s]<br><u>702</u> | リンク状態<br><u>703</u> | 重み<br>704 |

|---------------------|-----------------------------|---------------------|-----------|

| 0                   | 6000                        | 1                   | 1         |

| 1                   | 4000                        | 1                   | 2         |

## 【図5】

FIG. 5

ドライブ設定状態管理テーブル <u>144</u>

| ドライブ#<br><u>501</u> | 完了状態<br><u>502</u> | 結果状態<br><u>503</u> |

|---------------------|--------------------|--------------------|

| 0                   | 0                  | 0                  |

| 1                   | 0                  | 0                  |

| 2                   | 1                  | 1                  |

|                     |                    |                    |

# 【図8】

FIG. 8

アドレス変換テーブル <u>147</u>

| Tag#<br>801 | Path#<br>802 | 実メモリアドレス<br><u>803</u> | コマンド指定メモリアドレス<br><u>804</u> |

|-------------|--------------|------------------------|-----------------------------|

| 1           | 1            | 0x00000000_00040000    | 0x0000A000_00040000         |

| 2           | 0            | 0x00000000_00080000    | 0x0000B000_00080000         |

|             |              |                        |                             |

## 【図6】

FIG. 6

ドライブ初期設定管理テーブル <u>145</u>

| ドライブ#<br><u>601</u> | Bus#<br>602 | Device#<br>603 | Function#<br>604 | Base address<br>register<br>605 | MSI table<br>register<br>606 |

|---------------------|-------------|----------------|------------------|---------------------------------|------------------------------|

| 0                   |             |                |                  |                                 |                              |

| 1                   |             |                |                  |                                 |                              |

| 2                   |             |                |                  |                                 |                              |

|                     |             |                |                  |                                 |                              |

## 【図9】

FIG. 9

コマンド管理テーブル <u>148</u>

| Tag#<br>901 | ドライブ#<br><u>902</u> | Length<br>903 | コマンド指定メモリアドレス<br><u>904</u> | ドライブアドレス<br><u>905</u> |

|-------------|---------------------|---------------|-----------------------------|------------------------|

| 1           | 0                   | 0x20000       | 0x0000A000_00040000         | 0×00005000             |

| 2           | 1                   | 0x10000       | 0x0000B000_00080000         | 0x00001000             |

|             |                     |               | ***                         |                        |

【図10】

【図11】

FIG. 10 CPU <u>115</u> 内部CPU <u>114</u> Start S501 ドライブ問合せ 返却 S503 テーブルを更新 未設定ドライブ? S505 初期設定指示 初期設定 返却 \_S508 テーブルを更新 S511 成功? 失敗を登録 成功を登録 End

FIG. 11

【図12】

【図14】

# 【図15】

FIG. 15

【図16】

FIG. 16

全体アドレス管理テーブル 1600

| CTL#<br>1601 | Path#<br>1602 | Start address<br>1603 | Size<br>1604        |

|--------------|---------------|-----------------------|---------------------|

| 0            | 0             | 0x0000A000_00000000   | 0x00001000_00000000 |

| 0            | 1             | 0x0000B000_00000000   | 0x00001000_00000000 |

| 1            | 0             | 0x0000C000_00000000   | 0x00001000_00000000 |

| 1            | 1             | 0x0000D000_00000000   | 0x00001000_00000000 |

【図17】

FIG. 17

### 第1のスイッチアドレス管理テーブル <u>1700A</u>

| Path#<br>1701A | Start address<br>1702A | Size<br><u>1703A</u> |  |

|----------------|------------------------|----------------------|--|

| 0              | 0x0000A000_00000000    | 0x00001000_00000000  |  |

| 1              | 0x0000B000_00000000    | 0x00001000_00000000  |  |

【図18】

FIG. 18

#### 第2のスイッチアドレス管理テーブル <u>1700B</u>

| Path#<br>1701B | Start address<br>1702B | Size<br><u>1703B</u> |  |

|----------------|------------------------|----------------------|--|

| 0              | 0x0000C000_00000000    | 0x00001000_00000000  |  |

| 1              | 0x0000D000_00000000    | 0x00001000_00000000  |  |

## フロントページの続き

(56)参考文献 特開2011-248662(JP,A)

特開2014-002545(JP,A)

特表2015-501501(JP,A)

(58)調査した分野(Int.CI., DB名)

G06F3/06-3/08

G06F13/10-13/14

G06F13/38-13/42